Dans le cadre de mes précédents articles, j’ai voulu parcourir de manière historique l’évolution de l’ordinateur depuis ses conceptions purement mécaniques puis électro-mécaniques et enfin électroniques. Nous nous sommes arrêtés la semaine passée au stade de la fin des années 1950 lorsque la révolution fondamentale due à l’ invention du transistor advint. Ceci mit en évidence le phénomène de la miniaturisation des machines, phénomène qui attira l’ attention du scientifique Gordon Moore qui formula la loi célèbre portant son nom : la loi de Moore. Penchons nous à présent sur cette question.

Dans une publication datée de 1965, Gordon Moore avança l’idée selon laquelle la puissance des machines électroniques, notamment des circuits intégrés, serait amenée à doubler chaque année. Cependant, dix ans après sa première annonce, le sage Moore, après mûre réflexion, ajusta son postulat. Il suggéra alors que ce doublement prodigieux se manifesterait tous les 18 mois. Bien que légèrement modifié, ce rythme reste à couper le souffle et témoigne d’une progression effrénée. Il convient de noter que cette thèse, bien qu’elle ne repose que sur une observation empirique, a été vérifié maintes fois par la suite. Toutefois, le visionnaire Moore, toujours réaliste, prévoyait qu’à l’horizon 2017, ce rythme effréné rencontrerait des obstacles insurmontables, dictés par les limites mêmes de la nature.

Moore, qui occupait alors le poste de directeur de la recherche et du développement chez Fairchild Semiconductor (et qui deviendra par la suite président d’Intel), a réalisé une analyse empirique notable concernant l’évolution des composants électroniques. En élaborant un graphique pour illustrer l’évolution des performances des mémoires, Moore a observé que la capacité des circuits intégrés avait effectivement doublé annuellement de 1959 à 1965. Sur la base de ces données, il a postulé que la capacité de traitement des ordinateurs augmenterait à un taux exponentiel. Il convient de noter que cette hypothèse, bien qu’ambitieuse, s’appuyait uniquement sur cinq points de données observées durant cette période. Moore a formalisé cette observation dans un article publié dans la revue « Electronics » intitulé « Cramming more components into integrated circuits ». L’importance de cette publication réside dans le fait qu’elle a servi de catalyseur à la communauté de recherche, les encourageant à envisager des avancées technologiques en anticipant une croissance continue des performances. En conséquence, cette hypothèse a joué un rôle crucial dans la stimulation et l’accélération des efforts d’innovation et de miniaturisation dans le domaine de l’électronique. L’augmentation de la densité des composants sur les circuits intégrés conduit à une amélioration notable des performances. Deux facteurs principaux expliquent cette corrélation. Premièrement, une réduction de la distance entre les transistors se traduit par une augmentation de la vitesse de traitement. Deuxièmement, une densité accrue permet l’intégration de fonctions supplémentaires directement sur le circuit. Ainsi, des fonctionnalités qui étaient auparavant assurées par des dispositifs distincts, tels que la carte graphique, le modem ou le contrôleur de mémoire, peuvent être incorporées au sein de la puce elle-même.

La remarquable prévision de Moore, suggérant que le nombre de transistors sur un microprocesseur doublerait environ tous les deux ans, semblait être en phase avec les observations empiriques. En 2007, on envisageait des processeurs enrichis de près de 15 milliards de transistors !

Des expérimentations effectuées au CEA-Leti de Grenoble en 1999 avaient mis en évidence un transistor CMOS d’une finesse de 18 nanomètres équivalant, pour le mettre en perspective, à une séquence d’environ 70 atomes. En regardant les standards de 2003, cette prouesse était sept fois plus avancée que les modèles industriels de l’époque. La densité potentielle de ce prototype aurait pu s’élargir jusqu’à 7 milliards de jonctions sur une superficie comparable à une monnaie d’1€. Néanmoins, il était à noter que ce travail était, à l’époque, principalement théorique, et sa mise en œuvre à grande échelle demeurait un challenge colossal. Parallèlement à ces avancées, l’aspect économique de l’innovation technologique ne pouvait être négligé. La loi de Rock, moins connue mais tout aussi pertinente à cette époque, suggérait que les coûts de fabrication d’un circuit intégré pourraient doubler tous les quatre ans. Cela était principalement dû aux contraintes croissantes du processus de photolithographie qui se heurtait progressivement à ses frontières technologiques. Pour illustrer cet état de fait, on citait l’investissement massif d’Intel en 2004 où l’entreprise avait consacré plus de 2 milliards de dollars à la modernisation de ses installations.

Le défi persistant dans la quête de miniaturisation résidait dans la photolithographie, qui nécessitait des rayonnements à longueur d’onde toujours plus réduite. Les avancées de cette période orientaient vers l’utilisation du spectre des rayons X, ce qui engendrait des complications en termes de focalisation efficace. Des prédictions antérieures, datant du milieu des années 1990, étaient sceptiques quant à la faisabilité de la production de transistors de dimension inférieure à 100 nm avec cette technique. Toutefois, malgré des percées qui eurent lieu par la suite et ramenant cette dimension à 20 nm, il semblait que l’industrie approchait d’une barrière technologique. Cette ultime frontière était souvent désignée, dans les cercles industriels de l’époque, par le terme évocateur : « the Wall ».

Mais où en est-on aujourd’hui ?

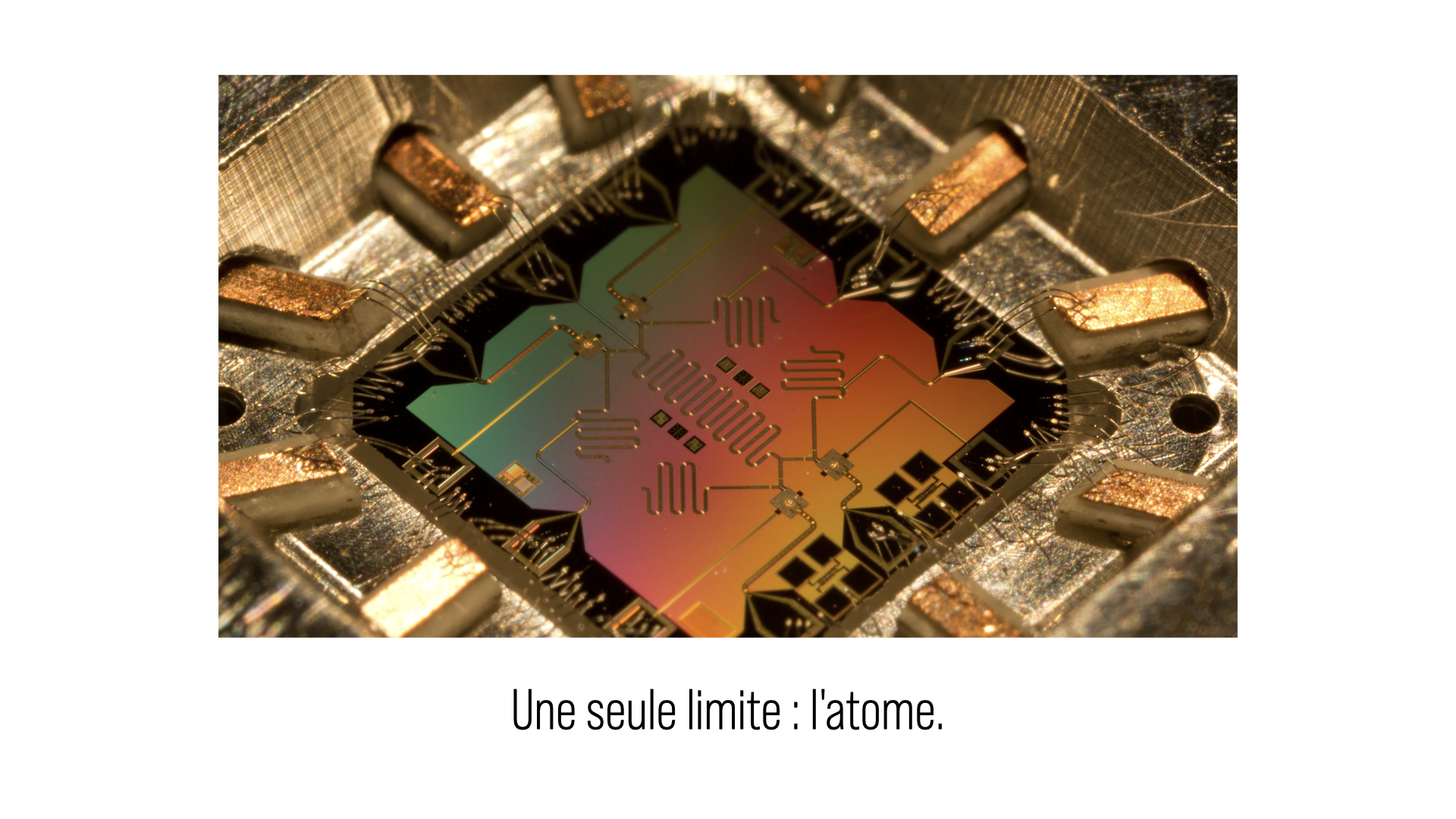

Au cours des dernières années, une décélération notable des avancées technologiques en matière de miniaturisation des composants électroniques a été observée. Cette tendance semble actuellement converger vers un plateau d’évolution technologique. Depuis les premières avancées qui ont permis de graver des composants à l’échelle micrométrique, l’industrie s’est progressivement approchée du niveau atomique, marquant ainsi une possible fin à cette quête de réduction dimensionnelle.

À titre illustratif, le microprocesseur initial commercialisé par Intel en 1971 contenait approximativement 2 300 transistors, avec une résolution gravimétrique de 10 µm. En revanche, les conceptions récentes ont vu l’intégration d’un nombre stupéfiant d’environ 4,3 milliards de transistors, représentant une augmentation factorielle de près de 1,87 million de fois. Toutefois, les experts du domaine ont, depuis plusieurs années, anticipé une halte inévitable dans cette progression. Cette stagnation est principalement attribuée à des contraintes intrinsèques de la physique et non de l’ industrie.

En particulier, en s’efforçant continuellement de minimiser la taille des composants électroniques, on se heurte inévitablement aux dimensions atomiques, où les principes de la mécanique quantique entrent en jeu, altérant le comportement standard des composants. Pour offrir une perspective, le transistor le plus récent, mesurant à peine 5 nm, s’aligne sur une séquence d’environ 10 atomes de silicium. En atteignant de telles dimensions, les électrons au sein du canal de silicium sont susceptibles de s’évader via un phénomène communément désigné sous le nom d’effet « tunnel ». Ce mécanisme peut, par conséquent, entraîner une diminution de la performance énergétique, ce qui pourrait avoir des implications négatives sur la vitesse d’exécution et même provoquer des erreurs fonctionnelles.

Un mur physique semble donc désormais atteint. Cependant, les chercheurs s’ orientent aujourd’hui vers une reformulation de l’ architecture même de l’ ordinateur en tentant de modifier fondamentalement les principes émis par Von Neumann et Turing dont nous avons parlé précédemment. Nous y reviendrons dans la suite de cette histoire passionnante.